The chapter concludes with a small discussion on further nonidealities of ΔΣ modulators, which are largely outside the scope of this text. The pros and cons for using a MASH converter versus a single-loop converter are given. Next, the signal processing of the MASH architecture, which is comprised of a cascade of basic ΔΣ modulators, is studied. The architectures of continuous-time and discrete-time ΔΣ modulators are presented, and the advantages and disadvantages of each design architecture are given in some detail.

The concept of oversampled converters and ΔΣ modulation and the basic loop dynamics are derived. We also discuss the impact of key performance parameters such as dynamic range, harmonic distortion, and thermal noise on the performance of the converter.

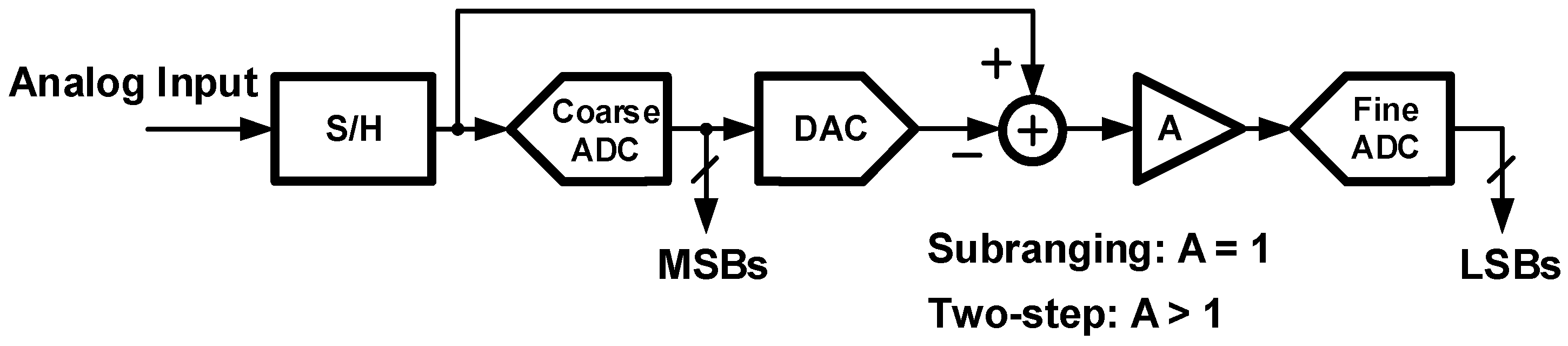

We also introduce the Nyquist converters and delve into the architectural details of the FLASH, pipelined, and folding ADC architectures. Topics such as aperture time accuracy, clock feedthrough, and charge injection and their impact on the signal-to-noise ratio (SNR) are also discussed. We discuss the main building blocks of ADCs, namely track-and-hold amplifiers and comparators. In this chapter, we discuss the various hardware architectures in which an analog-to-digital converter (ADC) can be implemented. This process could take place at baseband, as is the case of direct conversion receivers, or at intermediate frequency (IF) or low IF depending on the requirements and consequently on the receiver architecture pursued by the designers. Rouphael, in Wireless Receiver Architectures and Design, 2014 AbstractĪnalog to digital conversion is the process of transforming the signal from the analog domain to the digital domain.